# Comparative Study of Hall Effect Mobility in Inversion Layer of 4H-SiC MOSFETs With Nitrided and Phosphorus-Doped Gate Oxides

Munetaka Noguchi<sup>ID</sup>, Member, IEEE, Tomokatsu Watanabe<sup>ID</sup>, Hiroshi Watanabe, Koji Kita, and Naruhisa Miura

**Abstract**—In this study, the inversion layer mobility characteristics in Si-face 4H silicon carbide (SiC) metal-oxide-semiconductor field-effect transistors (MOSFETs) with nitrided and phosphorus-doped gate oxides were compared using Hall effect measurements. The inversion layer mobility was evaluated by applying a body bias and changing the temperature. The carrier scattering properties were determined for elevated temperatures (i.e., 473 K), at which point the impact of Coulomb scattering decreases and that of phonon scattering increases. The phonon-limited mobility of these MOSFETs was almost the same when plotted as a function of the effective normal electric field in the inversion layer, possibly representing the nature of the thermally grown  $\text{SiO}_2/\text{SiC}$  interface. On the basis of this finding, the effect of phonon scattering was separated from the inversion layer mobility. The MOSFETs exhibited a remarkable difference in Coulomb scattering: the MOSFETs with phosphorus-doped gate oxide exhibited a more rapid increase in Coulomb-limited mobility with increasing surface carrier density than did the MOSFETs with nitride gate oxide. This resulted from the effective suppression of Coulomb scattering in the inversion layer, which is one of the reasons why phosphorus-doped gate oxide achieves higher inversion layer mobility than nitrided gate oxide. These results show that the inversion layer mobility of SiC MOSFETs can be modeled using a conventional framework of phonon, Coulomb, and surface roughness scattering. Therefore, the suppression of Coulomb scattering is key to further improving the inversion layer mobility of SiC MOSFETs.

**Index Terms**—Hall effect mobility, inversion layer, metal-oxide-semiconductor field-effect transistor (MOSFET), nitrided gate oxide, phosphorus-doped gate oxide, silicon carbide (SiC).

Manuscript received August 6, 2021; revised September 29, 2021; accepted October 19, 2021. Date of current version December 1, 2021. The review of this article was arranged by Editor W. Saito. (Corresponding author: Munetaka Noguchi.)

Munetaka Noguchi, Tomokatsu Watanabe, Hiroshi Watanabe, and Naruhisa Miura are with the Advanced Technology Research and Development Center, Mitsubishi Electric Corporation, Hyogo 661-8661, Japan (e-mail: Noguchi.Munetaka@dh.MitsubishiElectric.co.jp; Watanabe.Tomokatsu@ab.MitsubishiElectric.co.jp; Watanabe.Hiroshi@dh.MitsubishiElectric.co.jp; Miura.Naruhisa@db.MitsubishiElectric.co.jp).

Koji Kita is with the Department of Materials Engineering, The University of Tokyo, Tokyo 113-8656, Japan (e-mail: kita@scio.t.u-tokyo.ac.jp).

Color versions of one or more figures in this article are available at <https://doi.org/10.1109/TED.2021.3125284>.

Digital Object Identifier 10.1109/TED.2021.3125284

## I. INTRODUCTION

**S**i-FACE 4H silicon carbide (SiC) metal-oxide-semiconductor field-effect transistors (MOSFETs) have been widely developed because of the high breakdown electric field and high thermal conductivity of their materials, which are suitable for power devices. Although nitrided gate oxide formed by thermal oxidation and subsequent nitridation treatment is usually employed to improve the inversion layer mobility [1], [2], the field-effect mobility remains as low as  $30 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$ . Alternatives such as phosphorus-doped [3]–[5], boron-doped [6], [7], or barium-doped [8]–[10] gate oxides are known to improve the field-effect mobility. For example, phosphorus-doped gate oxide achieves approximately three times higher field-effect mobility than that of nitrided gate oxide for a gate oxide electric field of 3 MV/cm [3]. In the case of the phosphorus-doped gate oxide, near-interface traps (NITs) at the  $\text{SiO}_2/\text{SiC}$  interface are eliminated [4]. This probably occurs because of the incorporation of P atoms in the  $\text{SiO}_2$  (the concentration of which can reach as high as  $2 \times 10^{21} \text{ cm}^{-3}$ ) and the reduction of strain at the interface. Despite the inferior field-effect mobility of nitrided gate oxide, it is widely used commercially because of its superior gate oxide reliability compared to alternative gate oxides. Hall effect measurements have been used extensively to identify the mobility-limiting factors in the inversion layer of SiC MOSFETs [11]–[20], as they allow the simultaneous evaluation of the inversion layer mobility ( $\mu_{\text{Hall}}$ ) and surface carrier density ( $N_S$ ) in the inversion layer. The inversion layer mobility can be evaluated without the impact of decreased  $N_S$  due to carrier trapping at the  $\text{SiO}_2/\text{SiC}$  interface. This is useful for SiC MOSFETs that have large interface trap densities near the conduction band edge [13], [14], [16], [18], [21]. Recent studies have revealed that the inversion layer mobility of Si-face 4H-SiC MOSFETs with nitrided gate oxide can be modeled in a conventional framework of phonon, Coulomb, and surface roughness scattering [15], [16], just as for Si MOSFETs [22], [23]. Although the framework itself is the same, the contributions of each scattering mechanism are different. The Coulomb-limited mobility ( $\mu_{\text{Coulomb}}$ ) of SiC MOSFETs

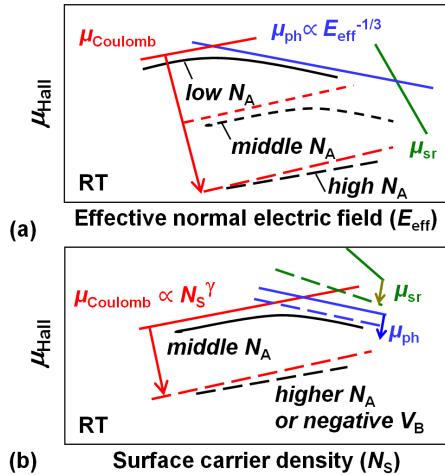

**Fig. 1.** Schematics of the framework for carrier scattering properties of SiC MOSFETs with nitrided gate oxide for various  $N_A$  and  $V_B$  at RT. (a)  $\mu_{\text{Hall}}$  as a function of  $E_{\text{eff}}$  and (b)  $\mu_{\text{Hall}}$  as a function of  $N_S$ .

exhibits unique features; it is strongly dependent on the acceptor concentration ( $N_A$ ) and/or the application of body bias ( $V_B$ ) to the p-type well region [15]–[17]. As  $N_A$  increases and/or a more negative  $V_B$  is applied,  $\mu_{\text{Coulomb}}$  decreases. Therefore, Coulomb scattering is possibly due to scattering centers located at and/or near the  $\text{SiO}_2/\text{SiC}$  interface, and not due to ionized impurities. Moreover,  $\mu_{\text{Coulomb}}$  is universally described by the inversion-carrier average distance from the  $\text{SiO}_2/\text{SiC}$  interface [17]. The framework of the carrier scattering properties of SiC MOSFETs with nitrided gate oxide is summarized in Fig. 1(a) and (b), which display  $\mu_{\text{Hall}}$  as a function of the effective normal electric field ( $E_{\text{eff}}$ ) and  $N_S$ , respectively, for various  $N_A$  and  $V_B$  [15], [16]. These were the cases at room temperature (RT). Here,  $\mu_{\text{Hall}}$  is determined by three factors: phonon-limited mobility ( $\mu_{\text{ph}}$ ), surface-roughness-limited mobility ( $\mu_{\text{sr}}$ ), and  $\mu_{\text{Coulomb}}$ . The latter is proportional to the power of  $N_S$ , which is attributed to the screening effect of the Coulomb scattering centers by inversion carriers [24], [25]. To further improve the inversion layer mobility of SiC MOSFETs, it is necessary to understand why MOSFETs with alternative gate oxides achieve higher field-effect mobility than MOSFETs with nitrided gate oxides. However, there are only a few studies on  $\mu_{\text{Hall}}$  for MOSFETs with alternative gate oxides [9], [10]. In particular, the  $\mu_{\text{Hall}}$  of MOSFETs with phosphorus-doped gate oxides has not been investigated yet.

In this study, to comprehensively understand the limiting factors of inversion layer mobility for nitrided gate oxide, we compare its performance to that of the MOSFETs with phosphorus-doped gate oxide using Hall effect measurements. The differences and similarities of these oxides are determined by evaluating the carrier scattering properties in these MOSFETs based on a recently proposed method [15], [16].

## II. EXPERIMENTAL METHODS

Planar-type Si-face 4H-SiC MOSFETs with Hall voltage terminals were fabricated as in our previous studies [16], [19]. The p-type well was formed by aluminum (Al)-doped p-type epitaxial layers or ion-implantation of Al in two different

doses. The  $N_A$  of the p-type epitaxial layers were approximately  $2 \times 10^{14}$ ,  $2 \times 10^{15}$ ,  $1 \times 10^{16}$ ,  $3 \times 10^{16}$ ,  $1 \times 10^{17}$ , and  $4 \times 10^{17}$  cm $^{-3}$ . The epitaxial layers were more than 4  $\mu\text{m}$ -thick, which were designed to be longer than the depletion region, and they were grown on 4° off-axis heavily doped n-type 4H-SiC (0001) substrates. Especially for the lowest  $N_A$  epitaxial layer such as  $2 \times 10^{14}$  cm $^{-3}$ , it is 11  $\mu\text{m}$ -thick and formed on the heavily-doped p-type layer to apply  $V_B$ . Nitrided gate oxide was formed by the processes of thermal oxidation and postoxidation nitridation treatment, which was carried out in NO (10% diluted in N<sub>2</sub>) at 1250 °C for 1 h. Phosphorus-doped gate oxide was formed by the processes of thermal oxidation followed by POCl<sub>3</sub> annealing at 1000 °C for 30 min using a conventional furnace [5]. Poly-Si was then deposited on the gate oxides. The n<sup>+</sup> region for the source, drain, and Hall voltage terminals was formed using heavily implanted nitrogen, with the Hall voltage terminals in the middle of the channel region. In order to apply  $V_B$ , the p<sup>+</sup> region was formed using heavily implanted Al on the p-type wells. The Ohmic contacts were formed using nickel silicide for both the n<sup>+</sup> and p<sup>+</sup> regions. The channel length and width were 500 and 150  $\mu\text{m}$ , respectively. When the ratio of the channel length to the channel width was more than 3 [26], a geometry factor of 0.95 was taken into account to correct for the geometry dependence of the Hall voltage. The  $N_S$  in the SiC MOS inversion layer was evaluated using the common assumption that the Hall scattering factor was unity and independent of  $N_S$  [9], [13]–[20].

### III. RESULTS AND DISCUSSION

### *A. Inversion Layer Mobilities at RT*

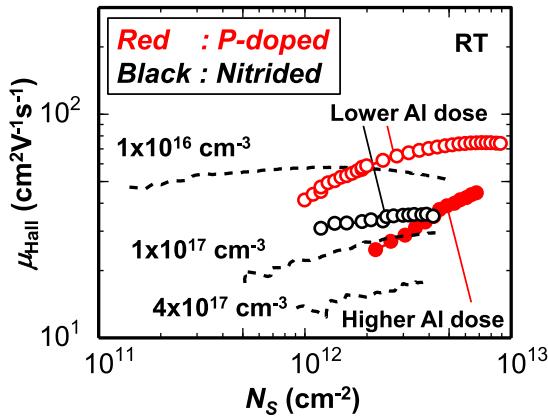

To understand the difference in  $\mu_{\text{Hall}}$  of the MOSFETs with nitrided and phosphorus-doped gate oxides, we compared their  $\mu_{\text{Hall}}$  values to various p-type wells at RT. Because the field-effect mobility of phosphorus-doped gate oxide is higher than that of nitrided gate oxide,  $\mu_{\text{Hall}}$  of the MOSFETs with phosphorus-doped gate oxide is expected to be higher than that of the MOSFETs with nitrided gate oxide. The field-effect mobility is affected by the carrier trapping effect at the  $\text{SiO}_2/\text{SiC}$  interface. Thus, it cannot represent the inversion layer mobility unless the carrier trapping is small. Therefore, the comparison of  $\mu_{\text{Hall}}$  enables the evaluation of the inversion layer mobility without the effect of carrier trapping. Fig. 2 shows  $\mu_{\text{Hall}}$  as a function of  $N_S$  for MOSFETs with nitrided (black lines and symbols) and phosphorus-doped gate (red symbols) oxide. The  $N_A$  values for the p-type epitaxial layers were  $1 \times 10^{16}$ ,  $1 \times 10^{17}$ , and  $4 \times 10^{17} \text{ cm}^{-3}$ , as shown in the figure. The open and closed symbols represent ion-implanted p-type wells with lower and higher Al doses, respectively. Here,  $V_B$  was set to 0 V. The depletion charge density ( $N_{\text{dep}}$ ) of the ion-implanted p-type well with a lower Al dose was approximately  $1.3 \times 10^{12} \text{ cm}^{-2}$ , which was nearly equal to that of the p-type epitaxial layers with an  $N_A$  of  $6 \times 10^{16} \text{ cm}^{-3}$ . The computation method is described in the rest of this section. Note that peak field-effect mobility of the MOSFETs with nitrided and phosphorus-doped gate oxides were 22 and  $87 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , respectively. Here, the MOSFETs were fabricated on ion-implanted p-type wells with

Fig. 2.  $\mu_{\text{Hall}}$  as a function of  $N_s$  at RT for the MOSFETs with nitrided (black lines and symbols) and phosphorus-doped (red symbols) gate oxide. They were fabricated on various p-type wells, as indicated in the figure.

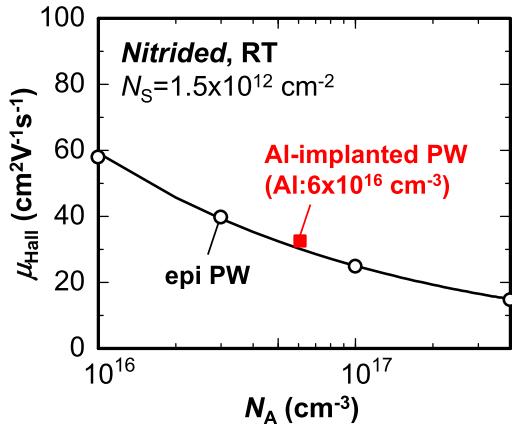

Fig. 3.  $\mu_{\text{Hall}}$  as a function of  $N_A$  at RT for the MOSFETs fabricated on p-type epitaxial layers (black) and ion-implanted p-type well with a lower Al dose (red). The gate oxides are nitrided oxide, and  $N_s$  is  $1.5 \times 10^{12} \text{ cm}^{-2}$ .

a lower Al dose. These values are comparable with previous reports [1], [3].

First, we confirmed that  $\mu_{\text{Hall}}$  of the MOSFETs exhibits the same tendency when fabricated on the p-type epitaxial layers and the ion-implanted p-type wells. For MOSFETs with nitrided gate oxide,  $\mu_{\text{Hall}}$  decreased as  $N_A$  increased. Additionally,  $\mu_{\text{Hall}}$  is proportional to the power of  $N_s$  for relatively high  $N_A$  (e.g.,  $1 \times 10^{17}$  and  $4 \times 10^{17} \text{ cm}^{-3}$ ) due to the strong effect of Coulomb scattering on  $\mu_{\text{Hall}}$  [15]–[17]. Here,  $\mu_{\text{Hall}}$  of the ion-implanted p-type well with a lower Al dose showed the same tendency. Fig. 3 shows  $\mu_{\text{Hall}}$  as a function of  $N_A$  at RT for the MOSFETs fabricated on p-type epitaxial layers and ion-implanted p-type well with a lower Al dose. The gate oxides are nitrided oxide, and  $N_s$  is  $1.5 \times 10^{12} \text{ cm}^{-2}$ . Here,  $N_A$  of the ion-implanted p-type well is regarded as  $6 \times 10^{16} \text{ cm}^{-3}$ . Its  $\mu_{\text{Hall}}$  was plotted on a close line for that of p-type epitaxial layer, and it was between that of the p-type epitaxial layer with an  $N_A$  of  $3 \times 10^{16}$  and  $1 \times 10^{17} \text{ cm}^{-3}$ . This is reasonable because  $\mu_{\text{Hall}}$  continuously decreased with increasing  $N_{\text{dep}}$  [17], and  $N_{\text{dep}}$  of the ion-implanted p-type well was between that of the p-type epitaxial layer with an  $N_A$  of  $3 \times 10^{16}$  and  $1 \times 10^{17} \text{ cm}^{-3}$ .

Next, the MOSFETs with different gate oxides were compared using MOSFETs fabricated on p-type wells with a lower

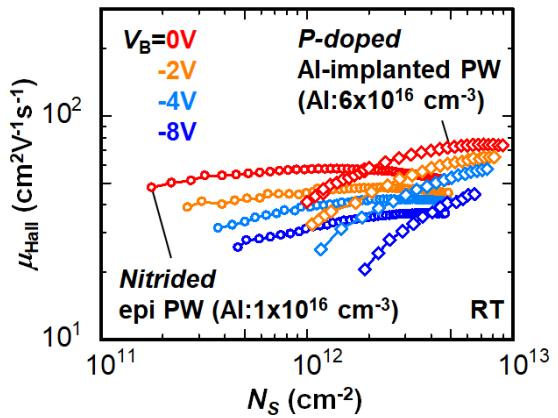

Fig. 4.  $V_B$  dependence on  $\mu_{\text{Hall}}$  as a function of  $N_s$  for the MOSFETs with nitrided and phosphorus-doped gate oxide at RT. The  $V_B$  was 0, -2, -4, and -8 V.

Al dose. The MOSFETs with phosphorus-doped gate oxide exhibited higher  $\mu_{\text{Hall}}$  than MOSFETs with nitrided gate oxide. Additionally, the variation in  $\mu_{\text{Hall}}$  for the MOSFETs with phosphorus-doped gate oxide was investigated. A higher Al dose resulted in the reduction of  $\mu_{\text{Hall}}$ , and the  $\mu_{\text{Hall}}$  was proportional to the power of  $N_s$ . By analogy to the nitrided gate oxide, these results suggest that a higher Al dose results in an increase in  $N_{\text{dep}}$ , and consequently, a decrease in  $\mu_{\text{Coulomb}}$ . This means that the contribution of Coulomb scattering to the total  $\mu_{\text{Hall}}$  increases for a higher Al dose. The  $N_s$  power-law coefficient of  $\mu_{\text{Hall}}$  was 0.54, which was slightly larger than that of nitrided oxide (0.24) when  $N_A$  was  $4 \times 10^{17} \text{ cm}^{-3}$  in the region with  $N_s > 2 \times 10^{12} \text{ cm}^{-2}$ .

These results indicate that the effect of Coulomb scattering is probably weakened by using phosphorus-doped gate oxide, but it is not fully removed. We evaluated the  $V_B$  dependence on  $\mu_{\text{Hall}}$  to confirm that in nitrided gate oxide  $\mu_{\text{Coulomb}}$  decreases as a more negative  $V_B$  is applied [15], [17]. The  $V_B$  dependence on  $\mu_{\text{Hall}}$  as a function of  $N_s$  for the MOSFETs with nitrided and phosphorus-doped gate oxide is shown in Fig. 4. They were measured at RT, and the  $V_B$  was 0, -2, -4, and -8 V. The circles and diamonds represent the nitrided and phosphorus-doped gate oxide, respectively. As shown in the figure, different p-type wells were used for each gate oxide. For the nitrided gate oxide, the MOSFET was fabricated on a p-type epitaxial layer with an  $N_A$  of  $1 \times 10^{16} \text{ cm}^{-3}$ . For phosphorus-doped gate oxide, the MOSFET was fabricated on an ion-implanted p-type well with a lower Al dose. As reported in [15] and [17],  $\mu_{\text{Hall}}$  of the MOSFETs with nitrided oxide decreased as a more negative  $V_B$  was applied. For the MOSFETs with phosphorus-doped gate oxide, the application of a more negative  $V_B$  was also found to result in a decrease in  $\mu_{\text{Hall}}$ . This result suggests that Coulomb scattering also has an impact on  $\mu_{\text{Hall}}$  in the region with low  $N_s$  for phosphorus-doped gate oxide. Because there was no overlap in  $\mu_{\text{Hall}}$  in the low  $N_s$  region as  $V_B$  became more negative, Coulomb scattering cannot be caused by ionized impurity scattering for either oxide. Therefore, the causes of Coulomb scattering for the phosphorus-doped gate oxide may originate at and/or near the  $\text{SiO}_2/\text{SiC}$  interface, which is also the case for nitrided gate oxide [17].

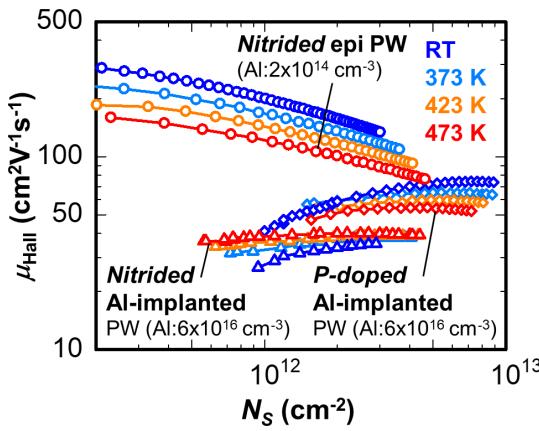

Fig. 5. Temperature dependence of  $\mu_{\text{Hall}}$  as a function of  $N_S$  for the MOSFETs with nitrided and phosphorus-doped gate oxide. The temperature was set to RT, 373, 423, and 473 K.

### B. Inversion Layer Mobilities at High Temperature

To understand  $\mu_{\text{Hall}}$  for both oxides over a wider temperature range, we carried out Hall effect measurements at elevated temperatures up to 473 K. The measurement of the temperature dependence of  $\mu_{\text{Hall}}$  enabled the investigation of the dominant scattering mechanisms in the inversion layer. This is because  $\mu_{\text{ph}}$  and  $\mu_{\text{Coulomb}}$  exhibit opposite temperature dependencies. An increase in temperature results in a decrease in  $\mu_{\text{ph}}$  [22], [23] and an increase in  $\mu_{\text{Coulomb}}$  [27]–[29]. The temperature dependence of  $\mu_{\text{Hall}}$  as a function of  $N_S$  for the MOSFETs with nitrided and phosphorus-doped gate oxide is shown in Fig. 5. The temperature was set to RT, 373, 423, and 473 K, and  $V_B$  was set to 0 V. For the nitrided gate oxide, the data represent a  $\mu_{\text{Hall}}$  of the p-type epitaxial layer with an  $N_A$  of  $2 \times 10^{14} \text{ cm}^{-3}$  and an ion-implanted p-type well with a lower Al dose. Different p-type wells were prepared to determine the temperature dependence of  $\mu_{\text{Hall}}$ , which in turn depended on the  $N_A$  of the p-type wells. For phosphorus-doped gate oxide, the data represent a  $\mu_{\text{Hall}}$  of the ion-implanted p-type well with a lower Al dose.

To determine whether phosphorus-doped gate oxide provides higher  $\mu_{\text{Hall}}$  than nitrided gate oxide at temperatures higher than RT, we compared  $\mu_{\text{Hall}}$  for the MOSFETs with both oxides at elevated temperatures. By comparing the MOSFETs fabricated on the ion-implanted p-type wells with a lower Al dose, we found that  $\mu_{\text{Hall}}$  for the MOSFETs with phosphorus-doped gate oxide was higher than that for the MOSFETs with nitrided gate oxide at temperatures between RT and 473 K. Additionally, we found that the temperature dependence of  $\mu_{\text{Hall}}$  was different for the two gate oxides. For the MOSFETs with nitrided gate oxide,  $\mu_{\text{Hall}}$  increased with increasing temperature, indicating that  $\mu_{\text{Hall}}$  was mainly dominated by Coulomb scattering, the effect of which becomes weaker at higher temperatures. In contrast,  $\mu_{\text{Hall}}$  of the MOSFETs with phosphorus-doped gate oxide decreased with increasing temperature, suggesting that  $\mu_{\text{Hall}}$  was mainly dominated by phonon scattering, the effect of which becomes stronger at higher temperatures. However, even in the case of nitrided gate oxide, the contribution of Coulomb scattering can be suppressed by lowering  $N_A$ .

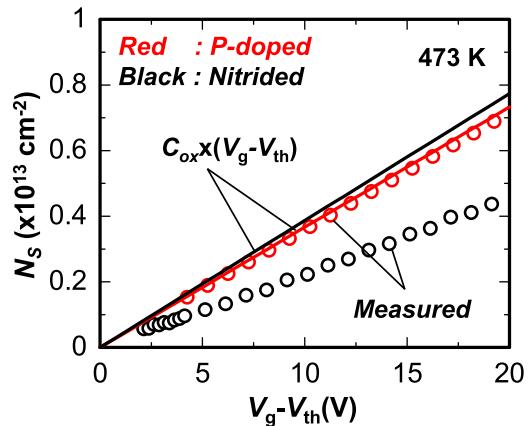

Fig. 6.  $N_S$  as a function of  $V_g - V_{\text{th}}$  for the MOSFETs with nitrided (black line and circles) and phosphorus-doped (red line and circles) gate oxide at 473 K.

to  $3 \times 10^{14} \text{ cm}^{-3}$  [15], [16]. As shown in Fig. 5,  $\mu_{\text{Hall}}$  decreased with increasing temperature, which indicates that  $\mu_{\text{Hall}}$  for nitrided gate oxide was mainly dominated by phonon scattering, as expected. Moreover, the temperature coefficient of  $\mu_{\text{Hall}}$  was on the order of  $-1$  for temperatures between 323 and 473 K. More precisely, it decreased as the temperature increased and reached as low as  $-1.52$  at 473 K. Here, the temperature coefficient of  $\mu_{\text{Hall}}$  was calculated for an  $E_{\text{eff}}$  of  $0.2 \text{ MV/cm}$ . Because this coefficient is less than  $-1$ , which is the theoretical value of acoustic phonon scattering [23], the conclusion that  $\mu_{\text{Hall}}$  is mainly dominated by phonon scattering is reasonable.

To understand the difference between nitrided and phosphorus-doped gate oxides, it is important to discuss the carrier trapping effect at the  $\text{SiO}_2/\text{SiC}$  interface. The carrier trapping effect can be determined by evaluating  $N_S$  as a function of the difference between the gate voltage and the threshold voltage ( $V_g - V_{\text{th}}$ ). Fig. 6 displays this relationship for the MOSFETs with nitrided (black) and phosphorus-doped (red) gate oxide at 473 K. The circles and lines represent the measured and ideal  $N_S$ , respectively. The MOSFETs were fabricated on ion-implanted p-type wells with a lower Al dose. The ideal  $N_S$  was calculated using  $C_{\text{ox}} \times (V_g - V_{\text{th}})$ , where  $C_{\text{ox}}$  corresponds to the capacitance of the gate oxide and  $V_{\text{th}}$  was defined by  $V_g$  where the linear extrapolation of the measured  $N_S$  was equal to zero. The difference between the slopes of the solid lines was due to the difference in the gate oxide thickness. The  $N_S$  of the MOSFETs with phosphorus-doped gate oxide was higher than that of the MOSFETs with nitrided gate oxide, as the former exhibited less carrier trapping at the  $\text{SiO}_2/\text{SiC}$  interface. The slope of  $N_S$  as a function  $V_g - V_{\text{th}}$  for the MOSFETs with phosphorus-doped gate oxide was nearly ideal, which suggests negligibly small carrier trapping in the region with  $N_S > 2 \times 10^{12} \text{ cm}^{-2}$ . This is consistent with a previous study [30]. This result represents that if there are unexpected  $V_{\text{th}}$  shifts during measurement like  $V_{\text{th}}$  shifts due to mobile ion drift, it would have only a limited effect on the extracted mobility characteristics. We also noticed that the slope of  $N_S$  as a function  $V_g - V_{\text{th}}$  for the MOSFETs with phosphorus-doped gate oxide at RT is 1.1 times larger than that expected by  $C_{\text{ox}}$ , which is different from the case

at 473 K. A previous study indicates a similar result at RT [30]. This might suggest that the Hall scattering factor at RT is below 0.91 which is less than one.

To understand the features of MOSFETs with phosphorus-doped gate oxide, it is helpful to compare them to those of alternative gate oxides such as Ba-doped gate oxide [10]. In the case of Ba-doped gate oxide,  $\mu_{\text{Hall}}$  does not improve in high  $N_S$  regions (e.g., with  $N_S = 2 \times 10^{12} \text{ cm}^{-2}$ ) when compared to nitrided gate oxide. In contrast, carrier trapping can be suppressed by Ba-doped gate oxide based on the free carrier ratio. These results indicate that the higher field-effect mobility in the MOSFETs with Ba-doped gate oxide can be attributed to the increased free carrier ratio [10] (i.e., the increase in  $N_S$ ). However, in the case of the phosphorus-doped gate oxide, both  $\mu_{\text{Hall}}$  in the high  $N_S$  region and  $N_S$  itself increased compared to those of the nitrided gate oxide. Therefore, both increments contribute to the higher field-effect mobility of phosphorus-doped gate oxide compared to nitrided gate oxide.

### C. Phonon-Limited Mobility at High Temperature

To discuss the mobility-limiting factors of  $\mu_{\text{Hall}}$ , it is common practice to describe  $\mu_{\text{Hall}}$  as a function of  $E_{\text{eff}}$  [15], [16], [22], [23], which is expressed by Takagi *et al.* [22]

$$E_{\text{eff}} = (q/\varepsilon_{\text{sic}})(N_{\text{dep}} + \eta \times N_S) \quad (1)$$

where  $q$  and  $\varepsilon_{\text{sic}}$  are the elementary charge and permittivity of 4H-SiC, respectively. In this study, the parameter  $\eta$  was set to 1/3, as in previous studies [15], [16], [22], [23]. For the p-type epitaxial layers,  $N_{\text{dep}}$  is defined by

$$N_{\text{dep}} = \sqrt{\left(2\varepsilon_{\text{sic}}N_A/q\right)\left\{\left(2kT/q\right)\ln\left(N_A/n_i\right) - V_B\right\}} \quad (2)$$

where  $k$ ,  $T$ , and  $n_i$  are Boltzmann's constant, the absolute temperature, and the intrinsic carrier concentration, respectively. For the ion-implanted p-type wells,  $N_{\text{dep}}$  was calculated using an equation based on Gauss's law in the region from the  $\text{SiO}_2/\text{SiC}$  interface to the edge of the depletion layer, which is expressed as

$$N_{\text{dep}} = (\varepsilon_{\text{si}o2} \times E_{\text{si}o2})/q - N_S \quad (3)$$

where  $\varepsilon_{\text{si}o2}$  and  $E_{\text{si}o2}$  are the permittivity of  $\text{SiO}_2$  and the gate oxide electric field at the  $\text{SiO}_2/\text{SiC}$  interface, respectively. We assumed that there was no charge in the oxide and at the  $\text{SiO}_2/\text{SiC}$  interface, resulting in a constant gate oxide electric field. In addition,  $N_S$  and  $E_{\text{si}o2}$  were calculated by considering the Al impurity profile analyzed by secondary ion mass spectrometry (SIMS). The total amount of Al dose was corrected by the intentionally implanted value. In addition, the electrical activation ratio of ion-implanted Al atoms was considered to be perfect since the total dose is not so high, and activation annealing was carried out at sufficiently high temperatures [31]. These quantities were calculated using commercially available TCAD, and  $N_S$  was the integration of inversion carriers over the depth at the middle of the MOSFETs.

To evaluate the carrier scattering properties in the inversion layer for the MOSFETs with nitrided and phosphorus-doped gate oxide, it is essential to evaluate  $\mu_{\text{ph}}$ . This is because

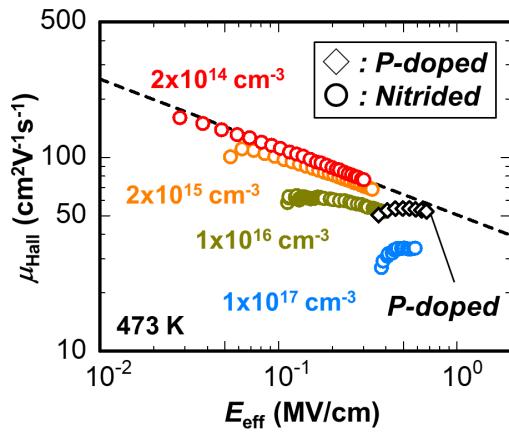

Fig. 7.  $\mu_{\text{Hall}}$  as a function of  $E_{\text{eff}}$  for the MOSFETs with nitrided (circles) and phosphorus-doped (diamonds) gate oxide at 473 K.

a recently proposed method enables the separation of mobility-limiting factors (e.g., phonons, surface roughness, and Coulomb scattering) using a formulated  $\mu_{\text{ph}}$  as a function of  $E_{\text{eff}}$  [15], [16]. It is still not clear whether  $\mu_{\text{ph}}$  at the  $\text{SiO}_2/\text{SiC}$  interface is affected by the gate oxides. To investigate this, we compared the MOSFETs for which  $\mu_{\text{Hall}}$  is mainly dominated by phonon scattering at high temperatures. Fig. 7 shows  $\mu_{\text{Hall}}$  as a function of  $E_{\text{eff}}$  for the MOSFETs with nitrided and phosphorus-doped gate oxide at 473 K. The circles and diamonds represent the nitrided and phosphorus-doped gate oxides, respectively. The  $N_A$  values for the MOSFETs with nitrided gate oxide were  $2 \times 10^{14}$ ,  $2 \times 10^{15}$ ,  $1 \times 10^{16}$ , and  $1 \times 10^{17} \text{ cm}^{-3}$ . In the MOSFETs with phosphorus-doped gate oxide, there was an ion-implanted p-type well with a lower Al dose. Here,  $V_B$  was set to 0 V.

To formulate  $\mu_{\text{ph}}$  for the nitrided gate oxide and determine the  $N_A$  dependence of  $\mu_{\text{Hall}}$ , we first focus on  $\mu_{\text{Hall}}$  of the MOSFETs with nitrided gate oxide. For the MOSFETs with nitrided gate oxide, the  $\mu_{\text{Hall}}$  values of the MOSFETs with  $N_A$  of  $2 \times 10^{14}$  and  $2 \times 10^{15} \text{ cm}^{-3}$  were plotted on almost the same line, which is an indication that  $\mu_{\text{Hall}}$  was very close to  $\mu_{\text{ph}}$ . Assuming  $\mu_{\text{Hall}}$  of the MOSFETs with an  $N_A$  of  $2 \times 10^{14} \text{ cm}^{-3}$  was equal to  $\mu_{\text{ph}}$  resulted in

$$\mu_{\text{ph}} = 51.8 \times E_{\text{eff}}^{-0.33} \quad (4)$$

where  $\mu_{\text{ph}}$  and  $E_{\text{eff}}$  have units of  $\text{cm}^2\text{V}^{-1}\text{s}^{-1}$  and  $\text{MV}/\text{cm}$ , respectively. The  $E_{\text{eff}}$  power-law coefficient of  $-0.33$  is very similar to the theoretical value of  $\mu_{\text{ph}}$  (i.e.,  $-1/3$ ) when the inversion carriers only occupy the lowest subband [23]. This is consistent with the assumption that  $\mu_{\text{Hall}}$  was close to  $\mu_{\text{ph}}$ . Additionally, as the  $N_A$  is above  $2 \times 10^{15} \text{ cm}^{-3}$ ,  $\mu_{\text{Hall}}$  was lower than the estimated  $\mu_{\text{ph}}$ , which is represented by the dashed line in Fig. 7. This deviation from the estimated  $\mu_{\text{ph}}$  can be ascribed to the Coulomb scattering effect at 473 K.

Next, we compared the estimated  $\mu_{\text{ph}}$  for the MOSFETs with nitrided gate oxide with the  $\mu_{\text{Hall}}$  of the MOSFETs with phosphorus-doped gate oxide. The  $\mu_{\text{Hall}}$  in the high  $E_{\text{eff}}$  region was very close to the line representing the estimated  $\mu_{\text{ph}}$  for the MOSFETs with nitrided gate oxide. This suggests that  $\mu_{\text{ph}}$  at the  $\text{SiO}_2/\text{SiC}$  interface was not affected by the nitrided and phosphorus-doped gate oxide. To confirm this,

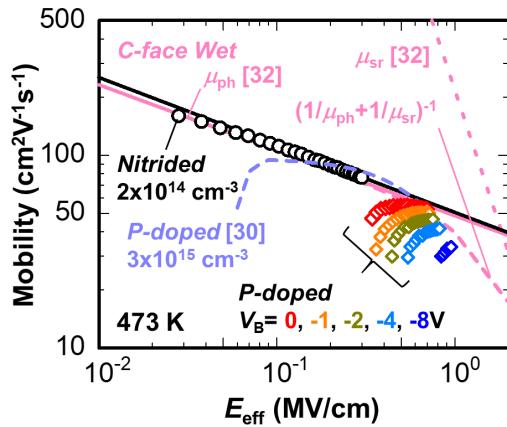

Fig. 8. Inversion layer mobility as a function of  $E_{\text{eff}}$  for the MOSFETs with nitrided, phosphorus-doped, and wet oxide at 473 K.  $\mu_{\text{ph}}$ ,  $\mu_{\text{sr}}$ , and a universal curve calculated by these mobilities are plotted based on [32].

we compared  $\mu_{\text{Hall}}$  as a function of  $E_{\text{eff}}$  to previously reported effective mobilities in the inversion layer of SiC MOSFETs. The inversion layer mobility as a function of  $E_{\text{eff}}$  for the MOSFETs with nitrided, phosphorus-doped, and wet gate oxides at 473 K is shown in Fig. 8. In the figure, the symbols represent our experimental results on  $\mu_{\text{Hall}}$  for nitrided and phosphorus-doped gate oxides. The variables  $\mu_{\text{ph}}$  and  $\mu_{\text{sr}}$ , as well as a universal curve calculated by these mobilities (i.e., the inverse of  $1/\mu_{\text{ph}} + 1/\mu_{\text{sr}}$ ), are plotted as magenta lines based on a formula for the C-face SiC MOSFETs with wet oxide [32]. The  $N_A$  is shown in the figure, and the p-type well for the MOSFETs with phosphorus-doped gate oxide was the same as in Fig. 7. To determine the change in  $\mu_{\text{Hall}}$  when  $N_{\text{dep}}$  becomes larger, the  $V_B$  dependence of the MOSFETs with phosphorus-doped gate oxide is also shown. Here,  $V_B$  was set to 0, -1, -2, -4, and -8 V. The  $\mu_{\text{ph}}$  of Si-face SiC MOSFETs with nitrided gate oxide, as shown by the black solid line, was almost the same as that of the C-face SiC MOSFETs with wet oxide at 473 K. This is similar to what has already been pointed out at RT [32].

Moreover, for the Si-face SiC MOSFETs with phosphorus-doped gate oxide fabricated using a low  $N_A$  of  $3 \times 10^{15} \text{ cm}^{-3}$ , the inversion layer mobility also showed good agreement with the  $\mu_{\text{ph}}$  in the  $E_{\text{eff}}$  region between 0.2 and 0.6 MV/cm, as shown by the light blue dotted line in Fig. 8 [30]. This supports the fact that the  $\mu_{\text{ph}}$  of the phosphorus-doped gate oxide was very close to that of the nitrided gate oxide at 473 K. These observations represent the nature of  $\mu_{\text{ph}}$  at the thermally grown  $\text{SiO}_2/\text{SiC}$  interface that is not affected by nitrided and phosphorus-doped gate oxide. Based on these results, we concluded that the  $\mu_{\text{ph}}$  of the  $\text{SiO}_2/\text{SiC}$  interface was successfully observed for the MOSFETs with nitrided gate oxide by elevating the temperature to 473 K and significantly lowering the  $N_A$  to  $2 \times 10^{14} \text{ cm}^{-3}$ .

From the discussion above,  $\mu_{\text{Hall}}$  of the measured MOSFETs with phosphorus-doped gate oxide was probably limited by  $\mu_{\text{ph}}$  in the high  $E_{\text{eff}}$  region at 473 K when  $V_B$  was 0 V. As the applied  $V_B$  became more negative,  $\mu_{\text{Hall}}$  of the measured MOSFETs with phosphorus-doped gate oxide decreased and became lower than  $\mu_{\text{ph}}$ . This suggests that Coulomb scattering

also has an impact on  $\mu_{\text{Hall}}$ , and that surface roughness scattering might start to affect  $\mu_{\text{Hall}}$  because the calculated universal curve of the C-face SiC MOSFETs becomes lower than  $\mu_{\text{ph}}$  due to its effect in the high  $E_{\text{eff}}$  region over 1 MV/cm.

#### D. Carrier Scattering Properties at High Temperature

We have successfully formulated  $\mu_{\text{ph}}$  at the  $\text{SiO}_2/\text{SiC}$  interface at 473 K, and it is possible to extract its effect from  $\mu_{\text{Hall}}$  and precisely determine the carrier scattering properties using a recently proposed method [15], [16]. Based on Matthiessen's rule, the effect of phonon scattering and other scatterings, such as Coulomb and surface roughness scattering, can be distinguished by

$$1/\mu_{\text{Hall}} = 1/\mu_{\text{ph}} + 1/\mu_{\text{other}} \quad (5)$$

where  $\mu_{\text{other}}$  represents mobility, which is the total effect of the carrier scatterings other than phonon scattering. First, we discuss the  $N_A$  dependence of the carrier scattering properties for MOSFETs with nitrided gate oxide. Then we discuss the  $V_B$  dependence of the carrier scattering properties for MOSFETs with phosphorus-doped gate oxide. Both the increase in  $N_A$  and the application of negative  $V_B$  were aimed at increasing the  $N_{\text{dep}}$  in the inversion layer because they allow control over  $\mu_{\text{Coulomb}}$  in the MOSFETs with nitrided and phosphorus-doped gate oxide. Later in this section, on the basis of conventional frameworks for inversion layer mobility [15]–[17], [22], [23], [32], the dominant mobility-limiting factor of  $\mu_{\text{other}}$  is discussed in terms of Coulomb scattering at and/or near the  $\text{SiO}_2/\text{SiC}$  interface for both oxides. This is because  $E_{\text{eff}}$  is below 1 MV/cm, where surface roughness scattering is expected to have little impact on  $\mu_{\text{other}}$ . The validity of a conventional framework of scattering mechanisms is also discussed.

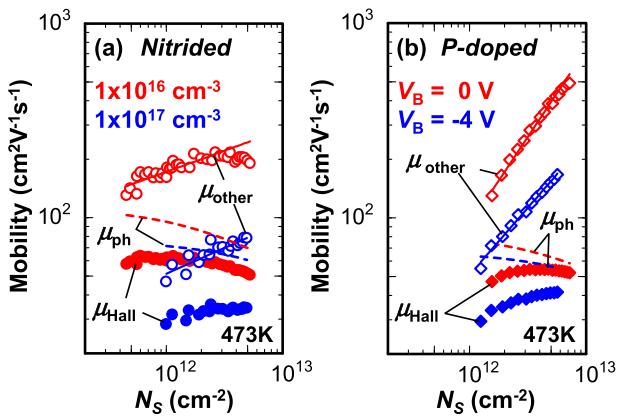

To investigate the carrier scattering properties of the MOSFETs with nitrided gate oxide at 473 K, the effects of phonons and other scatterings were extracted from  $\mu_{\text{Hall}}$ . Here, the  $N_A$  of the MOSFETs were  $1 \times 10^{16}$  and  $1 \times 10^{17} \text{ cm}^{-3}$ . Here,  $V_B$  was set to 0 V. Fig. 9(a) shows  $\mu_{\text{Hall}}$ ,  $\mu_{\text{ph}}$ , and  $\mu_{\text{other}}$  as functions of  $N_S$ . As  $N_S$  increased,  $\mu_{\text{other}}$  slightly increased for both  $N_A$ , which is possibly the result of the screening of Coulomb scattering centers by the inversion carriers. Specifically,  $\mu_{\text{other}}$  is proportional to the power of  $N_S$ , and its power-law coefficient ( $\gamma$ ) was 0.22 and 0.27 for  $N_A$  of  $1 \times 10^{16}$  and  $1 \times 10^{17} \text{ cm}^{-3}$ , respectively. As reported at RT [16],  $\gamma$  was slightly larger for higher  $N_A$ . For the MOSFETs with nitrided gate oxide at RT,  $\gamma$  of  $\mu_{\text{Coulomb}}$  for  $N_A = 1 \times 10^{16} \text{ cm}^{-3}$  was 0.2, and it increased with higher  $N_{\text{dep}}$  [17]. Thus, the features of  $\mu_{\text{other}}$  can be reasonably explained by the fact that the dominant limiting factor of  $\mu_{\text{other}}$  at 473 K is attributed to Coulomb scattering; its effect was not fully removed even at 473 K for MOSFETs with  $N_A$  of  $1 \times 10^{16}$  and  $1 \times 10^{17} \text{ cm}^{-3}$ . Additionally,  $\mu_{\text{Coulomb}}$  decreased with higher  $N_A$ , possibly because the inversion carriers moved closer to the  $\text{SiO}_2/\text{SiC}$  interface and the scattering probability at and/or near the  $\text{SiO}_2/\text{SiC}$  interface became larger.

From the plot in Fig. 9(a), the  $N_A$  dependence of the carrier scattering properties can be determined for MOSFETs with nitrided gate oxide. For an  $N_A$  of  $1 \times 10^{16} \text{ cm}^{-3}$ , the effect

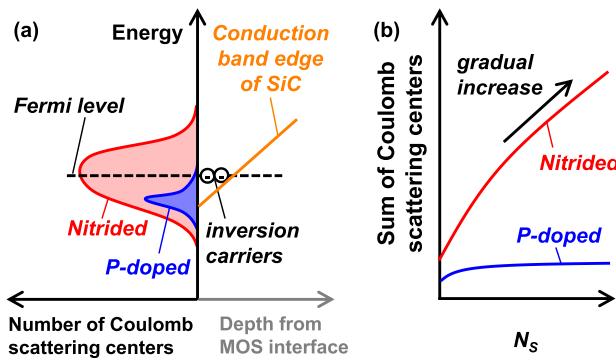

Fig. 9. (a)  $\mu_{\text{Hall}}$ ,  $\mu_{\text{ph}}$ , and  $\mu_{\text{other}}$  as a function of  $N_s$  for the MOSFETs with nitrided gate oxide at 473 K. The  $N_A$  was  $1 \times 10^{16} \text{ cm}^{-3}$  (red) and  $1 \times 10^{17} \text{ cm}^{-3}$  (blue). (b)  $\mu_{\text{Hall}}$ ,  $\mu_{\text{ph}}$ , and  $\mu_{\text{other}}$  as a function of  $N_s$  for the MOSFETs with phosphorus-doped gate oxide at 473 K. The p-type wells were the ion-implanted p-type wells with a lower Al dose.  $V_B$  of 0 V (red) and -4 V (blue) were applied.

of phonon scattering was more dominant than that of Coulomb scattering in the measured  $N_s$  region at 473 K, which is different from the case at RT. The effect of phonon scattering is dominant only in the high  $N_s$  region compared to the effect of Coulomb scattering at RT [15], [16]. However, for an  $N_A$  of  $1 \times 10^{17} \text{ cm}^{-3}$  at 473 K, the dominant scattering transitioned from Coulomb scattering to phonon scattering as  $N_s$  increased, which is also different from the case of RT. The effect of Coulomb scattering was dominant even in the region with high  $N_s$  at RT [15]. At RT, the effect of surface roughness scattering has a minor impact on  $\mu_{\text{Hall}}$  for MOSFETs with nitrided gate oxide in the  $E_{\text{eff}}$  region below 0.9 MV/cm [15], [16], and its impact may appear in the region with higher  $E_{\text{eff}}$  above 1 MV/cm [32]. At 473 K, the effect of surface roughness was much smaller than  $\mu_{\text{ph}}$  and  $\mu_{\text{Coulomb}}$  in the measured  $N_s$  region, which corresponded to the  $E_{\text{eff}}$  region below 0.6 MV/cm.

To investigate the carrier scattering properties of the MOSFETs with phosphorus-doped gate oxide at 473 K, the effects of phonons and other scatterings were extracted from  $\mu_{\text{Hall}}$ . Here, the p-type wells were ion-implanted p-type wells with a lower Al dose.  $V_B$  values of 0 and -4 V were applied. Fig. 9(b) shows  $\mu_{\text{Hall}}$ ,  $\mu_{\text{ph}}$ , and  $\mu_{\text{other}}$  as functions of  $N_s$ . As  $N_s$  increased,  $\mu_{\text{other}}$  rapidly increased. This behavior is different from that of MOSFETs with nitrided gate oxide. However,  $\mu_{\text{other}}$  is also proportional to the power of  $N_s$ , which is possibly the result of the screening of Coulomb scattering centers by the inversion carriers. Its  $\gamma$  values were 0.9 and 0.69 for  $V_B$  of 0 and -4 V, respectively; thus,  $\gamma$  is slightly smaller for more negative  $V_B$ , and it also decreases with increasing  $N_{\text{dep}}$  within the measured  $V_B$ . From the plot in Fig. 9(b), the  $V_B$  dependence of the carrier scattering properties can be determined for MOSFETs with phosphorus-doped gate oxide. Phonon scattering was more dominant than Coulomb scattering in the measured  $N_s$  region for  $V_B$  of 0 and -4 V. Although there was the effect of surface roughness scattering to some extent,  $\mu_{\text{sr}}$  was less dominant than  $\mu_{\text{ph}}$  and  $\mu_{\text{Coulomb}}$  in the measured  $N_s$  region, which corresponded to the  $E_{\text{eff}}$  region below 0.8 MV/cm. This is because  $\mu_{\text{other}}$  keeps increasing

Fig. 10.  $\mu_{\text{Hall}}$ ,  $\mu_{\text{ph}}$ , and  $\mu_{\text{other}}$  as a function of  $N_s$  for the MOSFETs with nitrided (black) and phosphorus-doped (red) gate oxides at 473 K. The p-type well was the ion-implanted p-type well with a lower Al dose.  $V_B$  of 0 V was applied.

with higher  $N_s$  and does not decrease even in the highest  $N_s$  region even though  $\mu_{\text{sr}}$  is expected to decrease with higher  $E_{\text{eff}}$  due to the increase in  $N_s$ . This is similar to the case of the nitrided gate oxide. Additionally,  $\mu_{\text{Coulomb}}$  decreased as  $V_B$  became more negative.

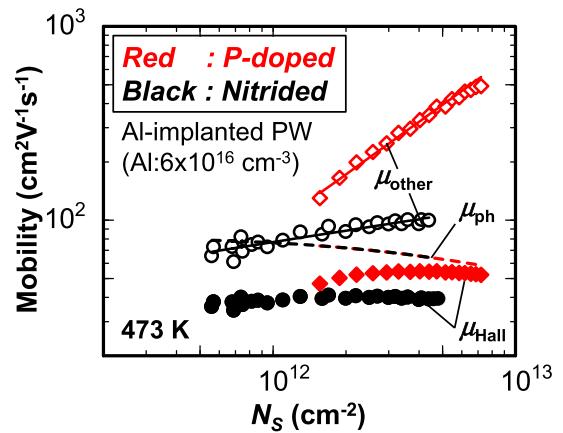

To simply discuss the difference in the carrier scattering properties of the MOSFETs with nitrided and phosphorus-doped gate oxides, the MOSFETs fabricated on ion-implanted p-type wells with a lower Al dose are compared. Fig. 10 shows  $\mu_{\text{Hall}}$ ,  $\mu_{\text{ph}}$ , and  $\mu_{\text{other}}$  as functions of  $N_s$  for both oxides at 473 K.  $V_B$  of 0 V was applied. The comparison between the MOSFETs with nitrided and phosphorous-doped gate oxides reveals a remarkable difference in the value of  $\gamma$ . The value of  $\gamma$  is 0.2 and 0.9, respectively. For both gate oxides, the increase in  $N_s$  resulted in higher  $\mu_{\text{Coulomb}}$  and weakened the relative impact of Coulomb scattering on the total  $\mu_{\text{Hall}}$ . However, in the case of the MOSFETs with phosphorus-doped gate oxide, the contribution of Coulomb scattering to the total  $\mu_{\text{Hall}}$  was quickly suppressed due to the larger  $\gamma$ , resulting in a smaller contribution of Coulomb scattering to the total  $\mu_{\text{Hall}}$ . As a result, the  $\mu_{\text{Hall}}$  of the MOSFETs with phosphorous-doped gate oxide was likely to be limited by  $\mu_{\text{ph}}$ . This is one of the reasons why a higher inversion layer mobility was achieved by the phosphorus-doped gate oxide. It is important to discuss the physical origin of the larger  $\gamma$  for the phosphorus-doped gate oxide. Although  $\gamma$  for the substrate ionized impurities was reported to be 1 for the Si MOSFETs [25], this was not the case for the SiC MOSFETs in this study because the relationship between  $\mu_{\text{other}}$  and  $N_s$  changed with different  $V_B$ . So, even for phosphorus-doped gate oxide, it is expected that the causes of Coulomb scattering other than ionized impurities are not fully removed at or near the SiO<sub>2</sub>/SiC interface.

To interpret this difference in  $\gamma$ , we referred to a previous report on Si MOSFETs related to remote Coulomb scattering [25]. In that study, it was pointed out that a gradual increase in the number of scattering centers possibly results in a weaker  $N_s$  dependence of  $\mu_{\text{Coulomb}}$ . Remote Coulomb scattering is caused by the depletion charge at the poly-Si/SiO<sub>2</sub> interface, and it is not applicable to SiC MOSFETs for which

Fig. 11. (a) Schematic of assumed energy distribution of effective number of Coulomb scattering centers for nitrided and phosphorus-doped gate oxide. To display the Fermi level in the inversion layer, the conduction band edge of SiC in the inversion layer is also shown. (b) Schematic of sum of effective number of Coulomb scattering centers as a function of  $N_s$  for nitrided and phosphorus-doped gate oxide.

the gate oxide thickness is much thicker. However, by analogy, the weaker  $N_s$  dependence of  $\mu_{\text{Coulomb}}$  in SiC MOSFETs with nitrided gate oxide can be interpreted. Although the origin is unclear, one possible explanation is that the number of Coulomb scattering centers gradually increases with increasing  $N_s$  in the case of nitrided oxide. Because the increase in  $N_s$  corresponds to the elevation of the Fermi level in the inversion layer, this may result from the difference between the energy distribution of the number of Coulomb scattering centers of both oxides. Coulomb scattering centers may have some spatial distribution in the oxides and near the  $\text{SiO}_2/\text{SiC}$  interfaces, which affects the impact of each scattering center on  $\mu_{\text{Coulomb}}$ . So, it would be better to discuss the effective number of Coulomb scattering centers. The assumed energy distribution of the effective number of Coulomb scattering centers is schematically shown for both oxides in Fig. 11(a). Assuming that the screening effect on the Coulomb scattering centers is the same for nitrided and phosphorus-doped gate oxide, it is expected that there are a larger number of Coulomb scattering centers and their energy distribution is broader in nitrided gate oxide compared to phosphorus-doped gate oxide. If this is true, the sum of effective number of the Coulomb scattering centers should increase with the elevation of the Fermi level in the inversion layer and with increasing  $N_s$ , as schematically shown in Fig. 11(b). For an ion-implanted p-type well with a lower Al dose, phosphorus-doped gate oxide provided a higher  $\mu_{\text{Hall}}$  than nitrided gate oxide, at least in the region with  $N_s > 1.6 \times 10^{12} \text{ cm}^{-2}$  at 473 K. This means that the effective number of the Coulomb scattering centers in the phosphorus-doped gate oxide was smaller than that in the nitrided gate oxide in this region. The Fermi level in the inversion layer was close to or above the conduction band edge of bulk SiC [33], [34]. In contrast, the MOSFETs with phosphorus-doped oxide exhibited a stronger  $N_s$  dependence for  $\mu_{\text{Coulomb}}$ . This means that, as  $N_s$  increases, the effective number of Coulomb scattering centers may not increase as rapidly as that of nitrided oxide.

This interpretation ensures that mobility-limiting factors in the inversion layer of SiC MOSFETs can be modeled within a conventional framework of scattering mechanisms, such as phonon, Coulomb, and surface roughness scatter-

ing [15], [16], [22], [23], [32]. Although it has been argued that phonon scattering should not dominate the inversion layer mobility [20], our results suggest that it is not necessary to consider a novel framework of scattering mechanisms that is unique to SiC. However, the origin of the Coulomb scattering centers is unclear, and further investigation is required. For the MOSFETs with  $N_A$  between  $1 \times 10^{15}$  and  $1 \times 10^{16} \text{ cm}^{-3}$ ,  $\mu_{\text{Hall}}$  in the region with  $N_s < 3 \times 10^{11} \text{ cm}^{-2}$ , where Coulomb scattering is dominant, was nearly the same regardless of nitridation treatment at RT [14], [18]. This suggests that trapped charges near the  $\text{SiO}_2/\text{SiC}$  interface, the energy level of which is below the conduction band edge, are not the major cause of these Coulomb scattering centers [18]. Therefore, the Coulomb scattering centers eliminated by phosphorus-doped gate oxide already exist immediately after thermal oxidation, and these scattering centers cannot be removed by the nitridation treatment. Our results suggest that the inversion layer mobility of SiC MOSFETs can be further improved by eliminating the Coulomb scattering centers.

#### IV. CONCLUSION

We compared the characteristics of the inversion layer mobility in Si-face 4H-SiC MOSFETs with nitrided and phosphorus-doped gate oxides using Hall effect measurements. Carrier scattering properties in the inversion layer were evaluated at high temperatures (i.e., 473 K). The  $\mu_{\text{ph}}$  values of these MOSFETs were almost the same, possibly representing the nature of the thermally grown  $\text{SiO}_2/\text{SiC}$  interface. Moreover, a remarkable difference was found in the behavior of Coulomb scattering in these MOSFETs. The MOSFETs with phosphorus-doped gate oxide exhibited a more rapid increase in  $\mu_{\text{Coulomb}}$  as  $N_s$  increased, resulting in the suppressed contribution of Coulomb scattering to the total  $\mu_{\text{Hall}}$  compared to the MOSFETs with nitrided oxide. We found that the inversion layer mobility of SiC MOSFETs can be modeled in a conventional framework of phonon, Coulomb, and surface roughness scattering. The suppression of Coulomb scattering is expected to further improve the inversion layer mobility of SiC MOSFETs.

#### REFERENCES

- [1] G. Y. Chung *et al.*, "Improved inversion channel mobility for 4H-SiC MOSFETs following high temperature anneals in nitric oxide," *IEEE Electron Device Lett.*, vol. 22, no. 4, pp. 176–178, Apr. 2001, doi: [10.1109/55.915604](https://doi.org/10.1109/55.915604).

- [2] K. Fujihira *et al.*, "Characteristics of 4H-SiC MOS interface annealed in  $\text{N}_2\text{O}$ ," *Solid-State Electron.*, vol. 49, no. 6, pp. 896–901, Apr. 2005, doi: [10.1016/j.sse.2004.10.016](https://doi.org/10.1016/j.sse.2004.10.016).

- [3] D. Okamoto, H. Yano, K. Hirata, T. Hatayama, and T. Fuyuki, "Improved inversion channel mobility in 4H-SiC MOSFETs on Si face utilizing phosphorus-doped gate oxide," *IEEE Electron Device Lett.*, vol. 31, no. 7, pp. 710–712, Jul. 2010, doi: [10.1109/LED.2010.2047239](https://doi.org/10.1109/LED.2010.2047239).

- [4] D. Okamoto, H. Yano, T. Hatayama, and T. Fuyuki, "Removal of near-interface traps at  $\text{SiO}_2/4\text{H-SiC}$  (0001) interfaces by phosphorus incorporation," *Appl. Phys. Lett.*, vol. 96, pp. 203508-1–203508-3, May 2010, doi: [10.1063/1.3432404](https://doi.org/10.1063/1.3432404).

- [5] T. Watanabe, M. Noguchi, S. Tomohisa, and N. Miura, "Compatibility of  $\text{POCl}_3$  gate process with the fabrication of vertical 4H-SiC MOSFETs," *Mater. Sci. Forum*, vol. 1004, pp. 565–570, Jul. 2020, doi: [10.4028/www.scientific.net/MSF.1004.565](https://doi.org/10.4028/www.scientific.net/MSF.1004.565).

- [6] D. Okamoto, M. Sometani, S. Harada, R. Kosugi, Y. Yonezawa, and H. Yano, "Improved channel mobility in 4H-SiC MOSFETs by boron passivation," *IEEE Electron Device Lett.*, vol. 35, no. 12, pp. 1176–1178, Dec. 2014, doi: [10.1109/LED.2014.2362768](https://doi.org/10.1109/LED.2014.2362768).

[7] M. Cabello, V. Soler, J. Montserrat, J. Rebollo, J. M. Rafí, and P. Godignon, "Impact of boron diffusion on oxynitrided gate oxides in 4H-SiC metal-oxide-semiconductor field-effect transistors," *Appl. Phys. Lett.*, vol. 111, pp. 042104-1–042104-4, Jul. 2017, doi: [10.1063/1.4996365](https://doi.org/10.1063/1.4996365).

[8] D. J. Lichtenwalner *et al.*, "Electrical properties and interface structure of SiC MOSFETs with barium interface passivation," *Mater. Sci. Forum*, vol. 897, pp. 163–166, May 2017, doi: [10.4028/www.scientific.net/MSF.897.163](https://doi.org/10.4028/www.scientific.net/MSF.897.163).

[9] E. Fujita *et al.*, "Insight into enhanced field-effect mobility of 4H-SiC MOSFET with Ba incorporation studied by Hall effect measurements," *AIP Adv.*, vol. 8, pp. 085305-1–085305-6, Aug. 2018, doi: [10.1063/1.5034048](https://doi.org/10.1063/1.5034048).

[10] S. Sekine *et al.*, "Free carrier density enhancement of 4H-SiC Si-face MOSFET by Ba diffusion process and NO passivation," *Jpn. J. Appl. Phys.*, vol. 60, no. SB, pp. SBB08-1–SBB08-6, Feb. 2021, doi: [10.35848/1347-4065/abdf1e](https://doi.org/10.35848/1347-4065/abdf1e).

[11] H. Naik and T. P. Chow, "Study of mobility limiting mechanisms in (0001) 4H and 6H-SiC MOSFETs," *Mater. Sci. Forum*, vols. 679–680, pp. 595–598, Mar. 2011, doi: [10.4028/www.scientific.net/MSF.679-680.595](https://doi.org/10.4028/www.scientific.net/MSF.679-680.595).

[12] V. Uhnevinak *et al.*, "Comprehensive study of the electron scattering mechanisms in 4H-SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 62, no. 8, pp. 2562–2570, Aug. 2015, doi: [10.1109/TED.2015.2447216](https://doi.org/10.1109/TED.2015.2447216).

[13] G. Ortiz *et al.*, "Impact of acceptor concentration on electrical properties and density of interface states of 4H-SiC n-metal-oxide-semiconductor field effect transistors studied by Hall effect," *Appl. Phys. Lett.*, vol. 106, no. 6, pp. 062104-1–062104-5, Feb. 2015, doi: [10.1063/1.4908123](https://doi.org/10.1063/1.4908123).

[14] T. Hatakeyama *et al.*, "Characterization of traps at nitrided SiO<sub>2</sub>/SiC interfaces near the conduction band edge by using Hall effect measurements," *Appl. Phys. Exp.*, vol. 10, no. 4, pp. 046601-1–046601-4, Mar. 2017, doi: [10.7567/APEX.10.046601](https://doi.org/10.7567/APEX.10.046601).

[15] M. Noguchi, T. Iwamatsu, H. Amishiro, H. Watanabe, K. Kita, and S. Yamakawa, "Determination of intrinsic phonon-limited mobility and carrier transport property extraction of 4H-SiC MOSFETs," in *IEDM Tech. Dig.*, Dec. 2017, pp. 219–222, doi: [10.1109/IEDM.2017.8268358](https://doi.org/10.1109/IEDM.2017.8268358).

[16] M. Noguchi *et al.*, "Carrier transport properties in inversion layer of Si-face 4H-SiC MOSFET with nitrided oxide," *Jpn. J. Appl. Phys.*, vol. 58, no. 3, pp. 031004-1–031004-6, Mar. 2019, doi: [10.7567/1347-4065/aafc51](https://doi.org/10.7567/1347-4065/aafc51).

[17] M. Noguchi, T. Iwamatsu, H. Amishiro, H. Watanabe, K. Kita, and N. Miura, "Coulomb-limited mobility in 4H-SiC MOS inversion layer as a function of inversion-carrier average distance from MOS interface," *Jpn. J. Appl. Phys.*, vol. 59, no. 5, pp. 051006-1–051006-5, May 2020, doi: [10.35848/1347-4065/ab8b3c](https://doi.org/10.35848/1347-4065/ab8b3c).

[18] M. Noguchi, T. Iwamatsu, H. Amishiro, H. Watanabe, K. Kita, and N. Miura, "Hall effect mobility in inversion layer of 4H-SiC MOSFETs with a thermally grown gate oxide," *Jpn. J. Appl. Phys.*, vol. 58, no. SB, pp. SBB08-1–SBB08-6, Mar. 2019, doi: [10.7567/1347-4065/aafdf95](https://doi.org/10.7567/1347-4065/aafdf95).

[19] M. Noguchi, T. Iwamatsu, H. Amishiro, H. Watanabe, K. Kita, and S. Yamakawa, "Hall effect mobility for SiC MOSFETs with increasing dose of nitrogen implantation into channel region," *Jpn. J. Appl. Phys.*, vol. 57, no. 4S, pp. 04FR13-1–04FR13-4, Mar. 2018, doi: [10.7567/JJAP.57.04FR13](https://doi.org/10.7567/JJAP.57.04FR13).

[20] M. Sometani *et al.*, "Ideal phonon-scattering-limited mobility in inversion channels of 4H-SiC(0001) MOSFETs with ultralow net doping concentrations," *Appl. Phys. Lett.*, vol. 115, no. 13, pp. 132102-1–132102-5, Sep. 2019, doi: [10.1063/1.5115304](https://doi.org/10.1063/1.5115304).

[21] H. Yoshioka, T. Nakamura, and T. Kimoto, "Generation of very fast states by nitridation of the SiO<sub>2</sub>/SiC interface," *J. Appl. Phys.*, vol. 112, no. 2, pp. 024520-1–024520-6, Jul. 2012, doi: [10.1063/1.4740068](https://doi.org/10.1063/1.4740068).

[22] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFET's: Part I-effects of substrate impurity concentration," *IEEE Trans. Electron Devices*, vol. 41, no. 12, pp. 2357–2362, Dec. 1994, doi: [10.1109/16.337449](https://doi.org/10.1109/16.337449).

[23] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFET's: Part II-effects of surface orientation," *IEEE Trans. Electron Devices*, vol. 41, no. 12, pp. 2363–2368, Dec. 1994, doi: [10.1109/16.337450](https://doi.org/10.1109/16.337450).

[24] Y. Nakabayashi, T. Ishihara, J. Koga, M. Takayanagi, and S. Takagi, "New findings on inversion-layer mobility in highly doped channel Si MOSFETs," in *IEDM Tech. Dig.*, Dec. 2005, pp. 133–136, doi: [10.1109/IEDM.2005.1609287](https://doi.org/10.1109/IEDM.2005.1609287).

[25] Y. Nakabayashi, J. Koga, T. Ishihara, and S. Takagi, "Physical origins of surface carrier density dependence of interface- and remote-Coulomb scattering mobility in Si MOS inversion layer," in *Proc. Ext. Abstr. SSDM*, Sep. 2005, pp. 44–45, doi: [10.7567/SSDM.2005.B-2-4](https://doi.org/10.7567/SSDM.2005.B-2-4).

[26] D. K. Schroder, *Semiconductor Material and Device Characterization*, 3rd ed. Hoboken, NJ, USA: Wiley, 2015, p. 478.

[27] A. Pérez-Tomás *et al.*, "Field-effect mobility temperature modeling of 4H-SiC metal-oxide-semiconductor transistors," *J. Appl. Phys.*, vol. 100, no. 11, pp. 114508-1–114508-6, Dec. 2006, doi: [10.1063/1.2395597](https://doi.org/10.1063/1.2395597).

[28] S. Potbhare, N. Goldsman, A. Lelis, J. M. McGarrity, F. B. McLean, and D. Habersat, "A physical model of high temperature 4H-SiC MOSFETs," *IEEE Trans. Electron Devices*, vol. 55, no. 8, pp. 2029–2040, Aug. 2008, doi: [10.1109/TED.2008.926665](https://doi.org/10.1109/TED.2008.926665).

[29] K. Naydenov, N. Donato, and F. Udrea, "An advanced physical model for the Coulombic scattering mobility in 4H-SiC inversion layers," *J. Appl. Phys.*, vol. 127, no. 19, pp. 194504-1–194504-13, May 2020, doi: [10.1063/5.0002838](https://doi.org/10.1063/5.0002838).

[30] K. Ito, M. Horita, J. Suda, and T. Kimoto, "Universal mobility of electrons in SiC(0001)/SiO<sub>2</sub> systems with phosphorus treatment," in *Proc. Abstr. JSAP Spring Meeting*, Mar. 2020, pp. 12–252. [Online]. Available: <https://confit.atlas.jp/guide/event-img/jsap2020s/15p-A201-7/public/pdf?type=in>

[31] T. Kimoto and J. A. Cooper, *Fundamentals of Silicon Carbide Technology*. Hoboken, NJ, USA: Wiley, 2014, p. 198.

[32] T. Ohashi, Y. Nakabayashi, and R. Iijima, "Investigation of the universal mobility of SiC MOSFETs using wet oxide insulators on carbon face with low interface state density," *IEEE Trans. Electron Devices*, vol. 65, no. 7, pp. 2707–2713, Jul. 2018, doi: [10.1109/TED.2018.2836347](https://doi.org/10.1109/TED.2018.2836347).

[33] G. Pennington and N. Goldsman, "Self-consistent calculations for n-type hexagonal SiC inversion layers," *J. Appl. Phys.*, vol. 95, no. 8, pp. 4223–4234, Mar. 2004, doi: [10.1063/1.1687977](https://doi.org/10.1063/1.1687977).

[34] S. Takagi and M. Takenaka, "An extraction method of interface state density near conduction band edge at SiC MOS interfaces," in *Proc. Ext. Abstr. SSDM*, Sep. 2016, pp. 241–242, doi: [10.7567/SSDM.2016.E-3-04](https://doi.org/10.7567/SSDM.2016.E-3-04).